### University of Texas Rio Grande Valley

# ScholarWorks @ UTRGV

Theses and Dissertations - UTB/UTPA

8-2009

# Asynchronous designs on FPGA with soft error tolerance for security algorithms

Deepya Reddy Nalubolu University of Texas-Pan American

Follow this and additional works at: https://scholarworks.utrgv.edu/leg\_etd

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Nalubolu, Deepya Reddy, "Asynchronous designs on FPGA with soft error tolerance for security algorithms" (2009). Theses and Dissertations - UTB/UTPA. 1034. https://scholarworks.utrgv.edu/leg\_etd/1034

This Thesis is brought to you for free and open access by ScholarWorks @ UTRGV. It has been accepted for inclusion in Theses and Dissertations - UTB/UTPA by an authorized administrator of ScholarWorks @ UTRGV. For more information, please contact justin.white@utrgv.edu, william.flores01@utrgv.edu.

# ASYNCHRONOUS DESIGNS ON FPGA WITH SOFT ERROR TOLERANCE FOR SECURITY ALGORITHMS

A Thesis

by

DEEPYA REDDY NALUBOLU

Submitted to the Graduate School of the University of Texas-Pan American In partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

August 2009

Major Subject: Electrical Engineering

# ASYNCHRONOUS DESIGNS ON FPGA WITH

# SOFT ERROR TOLERANCE FOR

#### **SECURITY ALGORITHMS**

A Thesis by DEEPYA REDDY NALUBOLU

Approved as to style and content by:

Dr. Weidong Kuang

Chair of Committee

Dr. Hasina Huq

Committee Member

Dr. Sanjeev Kumar Committee Member

#### **ABSTRACT**

Nalubolu, Deepya Reddy., <u>Asynchronous Designs on FPGA with Soft Error Tolerance</u> for Security Algorithms. Master of Science (MS), August, 2009, 140 pp., references, 52 titles.

Asynchronous methodologies, such as Null Convention Logic (NCL), have tremendous potential in implementing digital logic. It is essential to design complex asynchronous circuits using commercial Electronic Design Automation (EDA) tools. The main focus of this thesis is to design NCL circuits using VHDL and implementing them on FPGAs. The major contributions of this thesis include:

- 1) Developing a methodology of designing NCL circuits with VHDL and applying it successfully to all practical designs in this thesis.

- 2) As an example, the NCL circuit for DES (Data Encryption Standard) algorithm has been designed and simulated using VHDL and the implementation issues on various FPGAs (Xilinx and Altera) have been investigated. Modification of the design has been done to minimize the amount of logic used.

- 3) An effective soft error tolerant scheme for asynchronous circuits on FPGAs is proposed, and successfully verified through software simulation and hardware implementation by introducing it into a DES round.

This thesis provides a starting point for further investigation of NCL circuits, in terms of VHDL modeling, FPGA implementations, and soft error tolerance.

#### **DEDICATION**

I am extremely overwhelmed to dedicate this thesis to my only four valuables. My mother, Sowjanya Nalubolu, my father, VenuGopal Reddy Nalubolu, my brother Vinay Reddy Nalubolu and my friend Vijay Ashwanth, who have been with me through thick and thin. I am made out of their discipline and commitment.

My parents always taught me the importance of education in one's life without whom I would have never anticipated for higher education abroad. Their kind guidance has helped me choose the right path in life. My brother and my friend were always encouraging and helped a lot in successfully finishing my thesis.

#### **ACKNOWLEDGMENTS**

The support for the project is a grant from the Department of Defense (DOD). I would like to thank the DOD for believing in the potential of students not only from highly reputed schools but also in schools for minority students. Without the backing up of the DOD, the ideas might not have come into existence. The Department of Electrical Engineering at UTPA would always be indebted to Government and private organizations for supporting its students. I would also like to thank Dr.Kuang, the grant principle investigator (PI) and thesis committee Chair. He is a kind and wonderful teacher who has given enough freedom to think and successfully implement things. Last but not the least I would thank the UTPA for giving me an excellent opportunity to study here without which I would not have met wonderful teachers and friends. I also thank the almighty for this being his will. I would like to convey my special thanks to Dr.Scott smith, Associate Professor, Department of Electrical Engineering, University of Arkansas for providing the basic material, the NCL library, based on which the thesis is constructed upon.

# TABLE OF CONTENTS

| Page                                                   |

|--------------------------------------------------------|

| ABSTRACT iii                                           |

| DEDICATIONiv                                           |

| ACKNOWLEDGEMENTv                                       |

| TABLE OF CONTENTS                                      |

| LIST OF TABLESx                                        |

| LIST OF FIGURESxi                                      |

| CHAPTER I. INTRODUCTION                                |

| 1.1 Data Encryption Standard Algorithm2                |

| 1.2 Implementation of DES on FPGA5                     |

| 1.3 Asynchronous Design Methodology                    |

| 1.4 Soft Errors and Digital Circuits8                  |

| 1.5 Thesis Objectives                                  |

| CHAPTER II. BACKGROUND WORK ON NULL CONVENTION LOGIC12 |

| 2.1 Completion Criteria                                |

| 2.2 Threshold Gates with Hysteresis                    |

| 2.3 NCL Pipeline                                       |

| 2.3.1 NCL Register                                     |

| 2.3.2 Completion Detection Circuitry                   |

|    | 2.3.3 NCL Combinational Circuit                                       | 20  |

|----|-----------------------------------------------------------------------|-----|

| 2  | 2.4 NCL Circuits Using CMOS Transistors                               | 21  |

| CH | APTER III. NCL CIRCUIT DESIGN WITH VHDL                               | .24 |

| 3  | .1 FPGA                                                               | 24  |

| 3  | 2.2 Design Flow used in the Thesis                                    | 26  |

| 3  | 3.3 NCL Circuits in VHDL                                              | 28  |

|    | 3.3.1 Data Type Called dual_rail_logic                                | 28  |

|    | 3.3.2 Threshold Gates with Hysteresis in VHDL                         | 29  |

|    | 3.3.3 NCL Dual-rail Registers & Completion Detection Circuits in VHDL | .30 |

|    | 3.3.4 Constructing Computational Blocks                               | 32  |

| 3  | .4 Simulation of a Simple NCL Pipeline                                | 33  |

| CH | APTER IV. ASYNCHRONOUS DES ALGORITHM USING NCL                        | .38 |

| 4  | .1 Initial Register                                                   | 39  |

| 4  | .2 Initial Round                                                      | 40  |

| 4  | .3 NCL Registers1-15                                                  | 41  |

| 4  | .4 Rounds1-14                                                         | 42  |

| 4  | .5 Round 15                                                           | 43  |

| 4  | .6 NCL Register17                                                     | 44  |

| 4  | .7 Final Round and Final Register                                     | 44  |

| 4  | .8 NCL DES Design on FPGAs                                            | 44  |

|    | 4.8.1 Xilinx Device                                                   | 45  |

|    | 4.8.2 Altera Devices                                                  | 45  |

| 4  | .9 Improvements in Asynchronous DES Design                            | 47  |

| 4.9.1 Design Modification to Utilize Internal RAM Elements47             |

|--------------------------------------------------------------------------|

| 4.9.2 Resource Utilization with RAM elements                             |

| 4.9.3 Resource Comparison Between Synchronous and Asynchronous Designs50 |

| CHAPTER V. SOFT ERROR AND NCL CIRCUITS52                                 |

| 5.1 SEUs in NCL                                                          |

| 5.1.1 SEUS in Semiconductor Circuits53                                   |

| 5.1.2 Generation and Propagation of Soft Errors in NCL54                 |

| 5.2 Study of NCL Pipeline for an SEU55                                   |

| 5.3 Tackling Soft Errors Using NCL Methodology57                         |

| 5.3.1 Soft Error Mitigation and Correction57                             |

| 5.3.2 Soft Error Tolerant Schemes in NCL                                 |

| CHAPTER VI. SOFT ERROR TOLERANT DESIGN USING FPGA61                      |

| 6.1 Introduction61                                                       |

| 6.2 Soft Error Tolerant Design                                           |

| 6.2.1 Circuit for Soft Error Tolerance                                   |

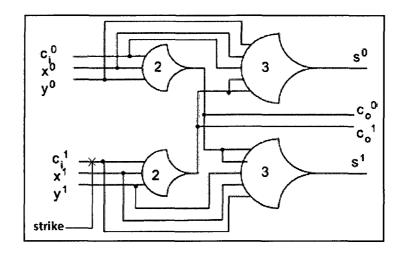

| 6.2.2 Case Study: NCL Full-adder as Computational Block                  |

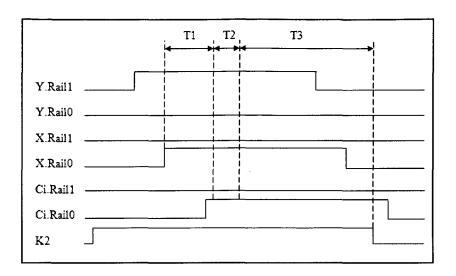

| 6.2.3 Generating Inputs and Strike                                       |

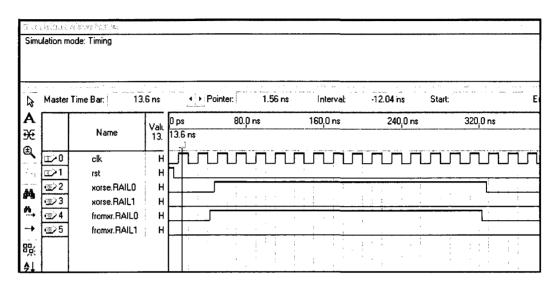

| 6.2.4 Simulation Results72                                               |

| 6.3 Experiments on FPGA Device                                           |

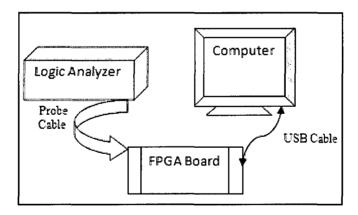

| 6.3.1 Experimental Set up79                                              |

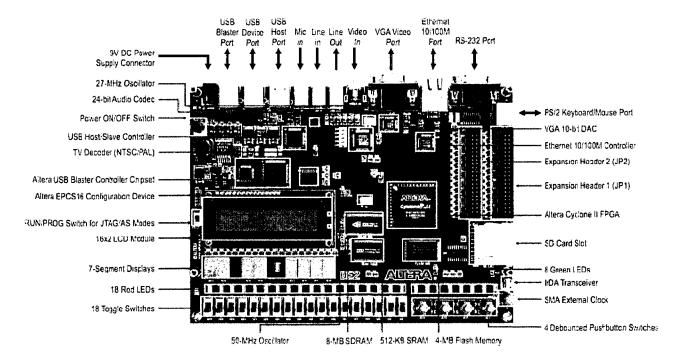

| 6.3.2 FPGA Board80                                                       |

| 6.3.3 Results81                                                          |

| CHAPTER VII. SOFT ERROR TOLERANT ASYNCHRONOUS DES DESIGN86               |

| 7.1 Asynchronous DES with Soft Error Tolerance     | 86  |

|----------------------------------------------------|-----|

| 7.2 Results Obtained                               | 88  |

| CHAPTER VIII. CONCLUSION AND FUTURE WORK           | 92  |

| REFERENCES                                         | 94  |

| APPENDIX A. DES ALGORITHM AND DESIGN UNITS IN VHDL | 98  |

| APPENDIX B. NCL LIBRARY                            | 106 |

| APPENDIX C. VHDL FILES USED FOR THE THESIS         | 116 |

| BIOGRAPHICAL SKETCH                                | 140 |

# LIST OF TABLES

| Table                                                                   | Page |

|-------------------------------------------------------------------------|------|

| 2.1: Dual-rail Encoding                                                 | 13   |

| 2.2: Twenty-Seven Fundamental NCL Gates and their Boolean Functions     | 16   |

| 4.1: Devices and Companies                                              | .44  |

| 4.2: Virtex5 Resources                                                  | 45   |

| 4.3: Resources used by DES Algorithm (dual-rail logic) on Xilinx Device | 45   |

| 4.4: Altera Device Resources                                            | .46  |

| 4.5: Resources used by DES Algorithm (dual-rail logic) on Altera Device | .46  |

| 4.6: Resources used by DES Algorithm with ROM on Altera Devices         | .50  |

| 4.7: FPGA Resources used by Different DES Designs                       | .51  |

| 6.1: Truth Table of a 1-bit Full Adder with Different States            | .66  |

# LIST OF FIGURES

| Figure                                                              | ge |

|---------------------------------------------------------------------|----|

| 1.1: Step by step procedure of DES                                  |    |

| 1.2: Metaphor of the bucket brigade a) synchronous b) asynchronous7 |    |

| 2.1: Weak Conditions for NCL Completeness of Input14                |    |

| 2.2: Different threshold gates                                      |    |

| 2.3: Basic NCL pipeline structure                                   |    |

| 2.4: 1-bit NCL register                                             |    |

| 2.5: n-bit completion detection circuitry                           |    |

| 2.6: NCL implementation of a) Inverter b) Exor gate c) Full-adder21 |    |

| 2.7: General Structure of a Static Gate                             |    |

| 2.8: Go to NULL and hold DATA transistor blocks                     |    |

| 2.9: Static th <sub>23</sub> gate                                   |    |

| 3.1: Basic resources of an FPGA                                     |    |

| 3.2: FPGA design flow                                               |    |

| 3.3: Design flow                                                    |    |

| 3.4: dual_rail_logic data-type                                      |    |

| 3.5: Behavioral description of th <sub>22</sub> in VHDL29           |    |

| 3.6: 1-bit NCL register in VHDL                                     |    |

| 3.7: Creating n-bit register from 1-bit register31                  |    |

| 3.8: VHDL code for a) Exor gate b) Full-adder            | 32 |

|----------------------------------------------------------|----|

| 3.9: NCL pipeline with exor gate                         | 33 |

| 3.10: VHDL code for the NCL pipeline with exor gate      | 34 |

| 3.11: a) initreg.vhd b) exor_dl.vhd c) finalreg.vhd      | 35 |

| 3.12: Quartus II software window                         | 36 |

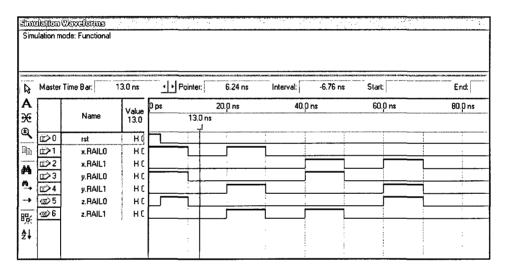

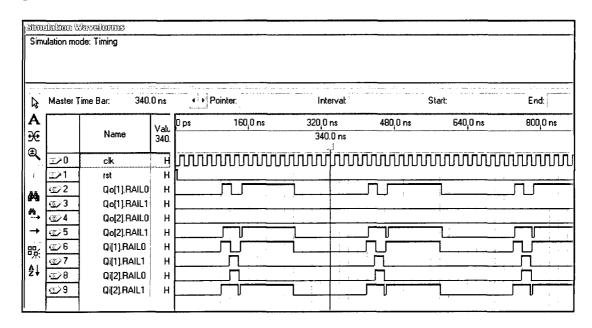

| 3.13: Simulation results of exor.vhd                     | 37 |

| 4.1: DES pipeline in NCL dual-rail logic                 | 39 |

| 4.2: Initial Register                                    | 39 |

| 4.3: Initial round in the DES pipeline                   | 40 |

| 4.4: S-box inputs and outputs                            | 41 |

| 4.5: The inside view of NCL register1-15                 | 42 |

| 4.6: Internal structure of rounds1-14                    | 43 |

| 4.7: NCL register17                                      | 43 |

| 4.8: Asynchronous DES round with S-boxes as RAM elements | 47 |

| 4.9: S-box as ROM                                        | 48 |

| 5.1: Mechanism of soft errors in semiconductor circuits  | 53 |

| 5.2: SEU generation in th <sub>23</sub> gate             | 55 |

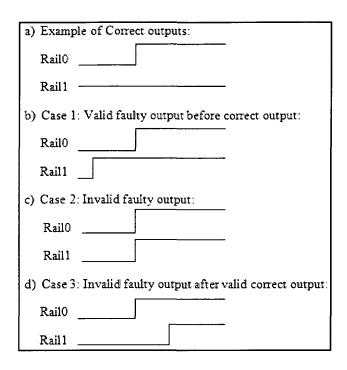

| 5.3: Different outputs during different strike timings   | 57 |

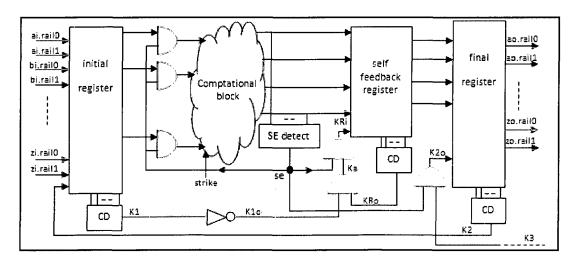

| 6.1: Soft error tolerant design                          | 62 |

| 6.2: Three scenarios to be tested for a full-adder       | 67 |

| 6.3: 1-bit dual-rail full-adder with strike              | 69 |

| 6.4: Modified full-adder incorporating strike            | 70 |

| 6.5: VHDL code for inducing a particle strike            | 70 |

| 6.6: Inputs and strike generator                                         | 71 |

|--------------------------------------------------------------------------|----|

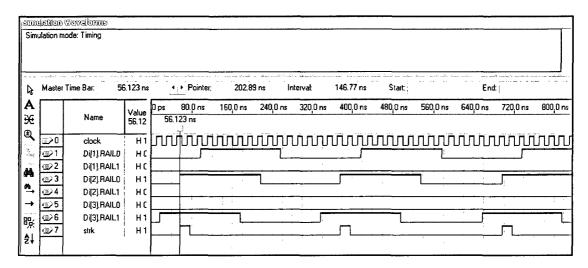

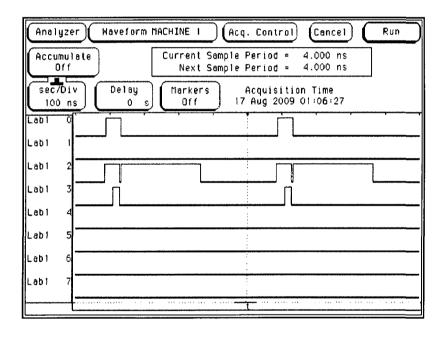

| 6.7: Simulation waveform of inputs & strike generator                    | 72 |

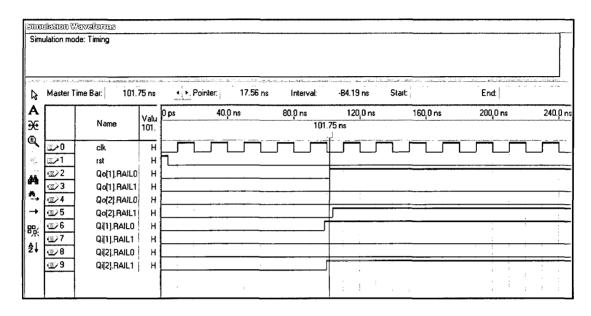

| 6.8: Simulation results without a strike                                 | 73 |

| 6.9: Simulation results during a strike at third clock cycle             | 73 |

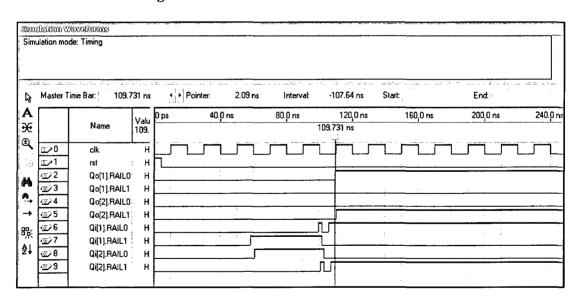

| 6.10: Simulation results when strike is placed at the first clock cycle  | 74 |

| 6.11: Simulation results when strike is placed at the second clock cycle | 74 |

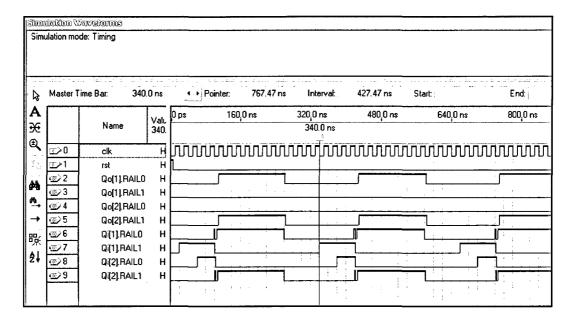

| 6.12: Simulation results when strike is placed at the third clock cycle  | 75 |

| 6.13: Simulation results when strike is placed at the fourth clock cycle | 76 |

| 6.14: Simulation results when strike is placed at the fifth clock cycle  | 76 |

| 6.15: Simulation results when strike is placed at the sixth clock cycle  | 77 |

| 6.16: Experimental set up                                                | 78 |

| 6.17: Laboratory experimental set up                                     | 79 |

| 6.18: The DE2 board                                                      | 30 |

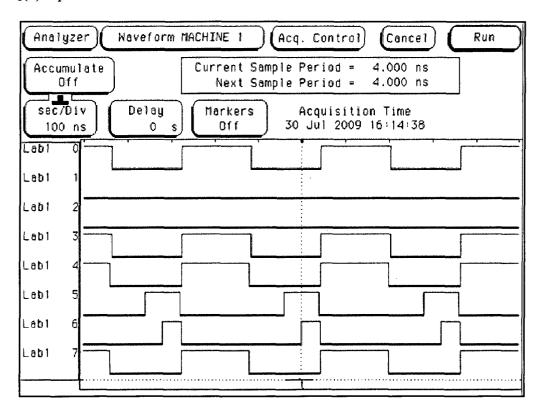

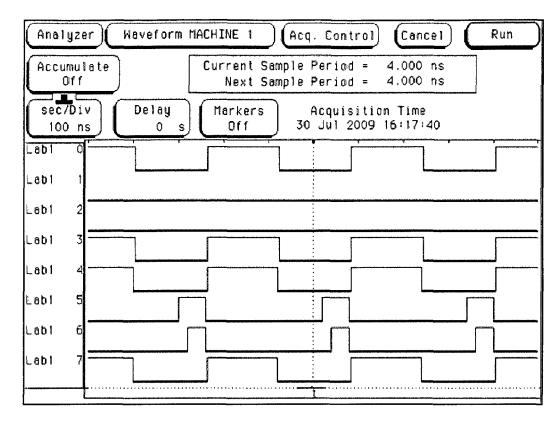

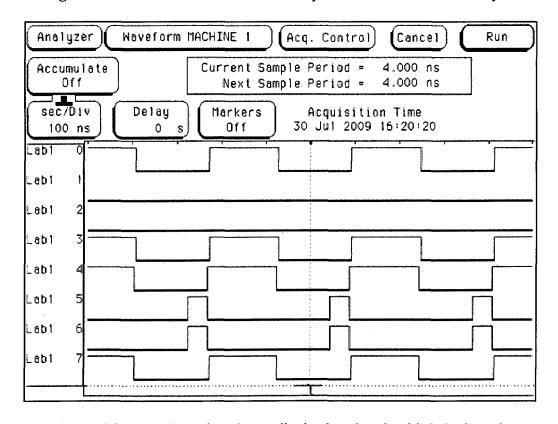

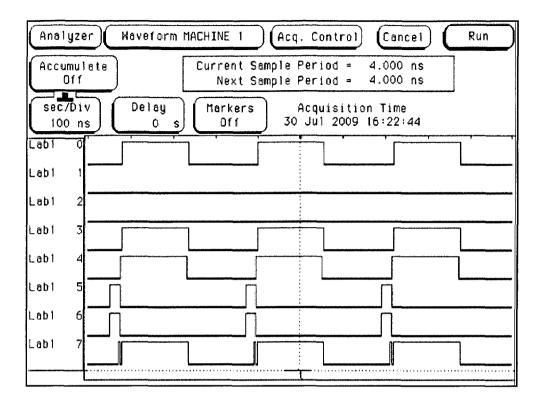

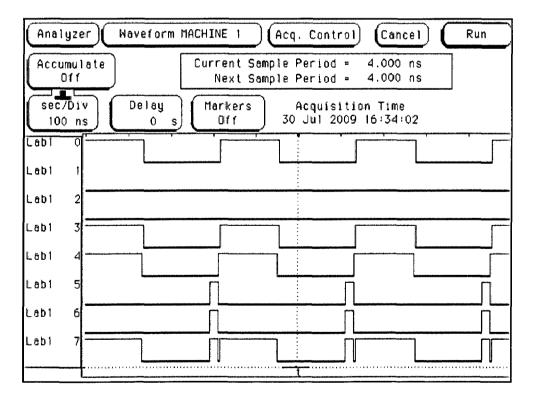

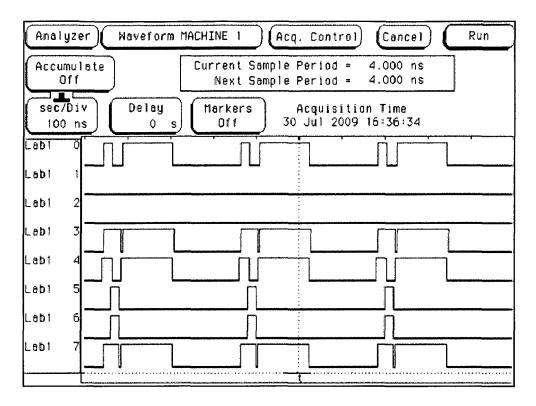

| 6.19: Actual results when strike is placed at the first clock cycle      | 82 |

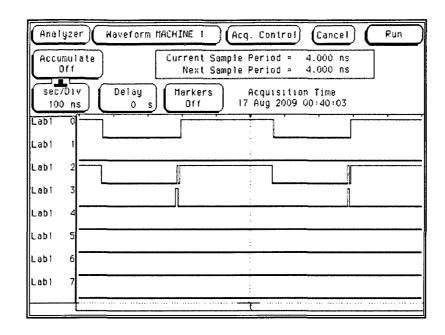

| 6.20: Actual results when strike is placed at the second clock cycle     | 33 |

| 6.21: Actual results when strike is placed at the third clock cycle      | 83 |

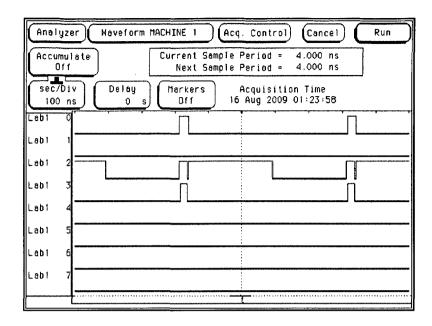

| 6.22: Actual results when strike is placed at the fourth clock cycle     | 84 |

| 6.23: Actual results when strike is placed at the fifth clock cycle      | 84 |

| 6.24: Actual results when strike is placed at the sixth clock cycle      | 85 |

| 7.1: Asynchronous DES with embedded soft error tolerant circuit          | 87 |

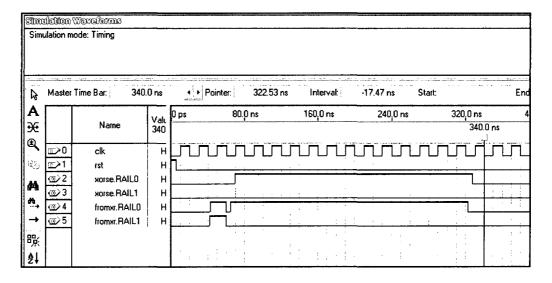

| 7.2: Simulation result for strike at first clock cycle                   | 88 |

| 7.3: Actual result for strike at first clock cycle                       | 89 |

| 7.4: Simulation result for strike at second clock cycle                  | 89 |

| 7.5: Actual result for strike at second clock cycle    | 89 |

|--------------------------------------------------------|----|

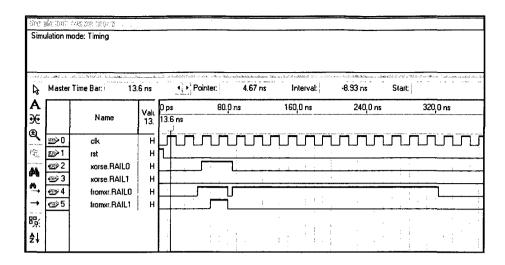

| 7.6: Simulation result for strike at third clock cycle | 91 |

| 7.7: Actual result for strike at third clock cycle     | 91 |

#### CHAPTER I

#### INTRODUCTION

Data Encryption Standard (DES) algorithm, a most widely used algorithm in the world is a cipher (a method for encrypting information) which was selected as an official Federal Information Processing Standard (FIPS) for the United States in 1976[1]. DES provided the basics for understanding block ciphers and their cryptanalysis. DES algorithm operates on a 64 bit plaintext using 56 bit key (actually 64 bit key, every 8<sup>th</sup> bit of the key is not used) thereby generating a 64 bit ciphertext which is the encrypted data.

A Field Programmable Gate Array (FPGA) is a semiconductor device that can be programmed or configured any number of times using a schematic design or a source code in HDL (hardware description language) that describe the user's hardware design [2]. FPGAs can be configured with dense logic and have very high logic capacity. Cryptographic algorithms like DES could be made to accommodate into the logic cells and the memory units of the FPGA since it also provides the advantage of updating and reprogramming any number of times in the future.

Asynchronous circuits [3] are digital circuits which operate without a clock unlike synchronous circuits whose operation is solely dependent on a clock signal.

Asynchronous circuits use handshaking protocols to communicate between modules or

parts of the circuits for the operations to be done in sequence. As these circuits have additional handshaking protocols other than logic, the entire circuit design will be undoubtedly large compared to their synchronous counterparts. Hence, the challenge to optimize these designs on the FPGA logic is inevitable.

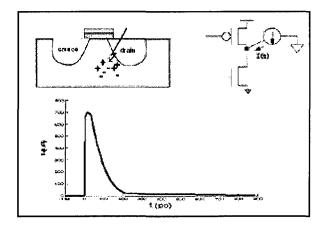

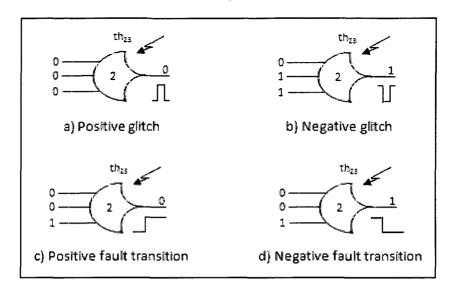

Soft errors, also called transient faults or single-event upsets (SEUs) are caused due to electrical noise or external radiation rather than design or manufacturing defects. As CMOS device sizes decrease, they are more easily affected by the low energy particles resulting from collisions between cosmic rays and particles in the atmosphere, potentially leading to a much higher rate of soft errors [4].

#### 1.1 Data Encryption Standard Algorithm

DES is a block cipher - meaning it operates on plaintext blocks of a given size (64-bits) and returns ciphertext blocks of the same size. DES algorithm has been the foundation for many of the future cryptographic algorithms. Since its creation, DES was considered as a basic cryptographic algorithm by the academia and has been researched to crack the algorithm, create similar algorithms which are robust. The algorithm is believed to be practically secure in the form of Triple DES (TDEA) [1].

DES algorithm takes plain text as a block of 64-bits and generates a cipher using a 64-bit key. In general, cryptography is used to protect data while it is being communicated between two points or while it is stored in a medium vulnerable to physical theft. Communication security provides protection to data by enciphering it at the transmitting point and deciphering it at the receiving point. Enciphering is the process of generating a cipher (encrypted data) using the data and the key while deciphering is

just the opposite which is getting the original data using the cipher and the key. This thesis focuses only on enciphering procedure since deciphering is just the opposite.

File security provides protection to data by enciphering it when it is recorded on a stored medium and deciphering it when it is read back from the stored medium. In the first case, the key must be available at the transmitter and receiver simultaneously during communication. In the second, case the key must be maintained and accessible for the duration of the storage period. Figure 1 shown below pictorially explains the step by step procedure of DES.

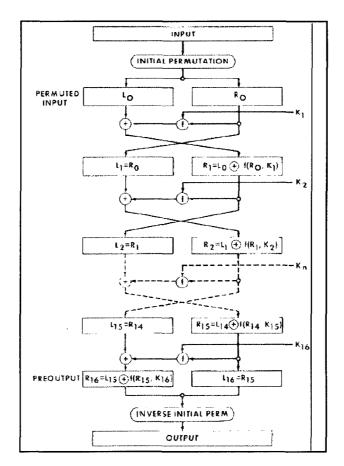

Figure 1.1 Step by step procedure of DES [5]

Here is a brief description of DES. The detailed description along with all the permutation and expansion tables, s-boxes and shift tables are presented in appendix A

The 64-bit data is applied with an initial permutation IP and the result is divided into two 32-bits, the left half as  $L_0$  and the right half as  $R_0$ . These  $L_0$  and  $R_0$  serve as the initial data from which further halves ( $L_1$ ,  $R_1$ ..... $L_{16}$ ,  $R_{16}$ ) are generated. The final cipher is generated from flipping and permuting  $L_{16}$  and  $R_{16}$ . The two equations which are used to generate  $L_i$  and  $R_i$  are  $L_i = R_{i-1}$  and  $R_i = L_{i-1} + f(R_{i-1}, K_i)$  which means next L is the present R and next R is obtained from present R and  $R_1$  is obtained from  $R_0$  and  $R_1$ , which is the first sub-key, after a series of steps mentioned below.

After as initial permutation, the 64-bit data is divided into 32-bits each as  $L_0$  and  $R_0$ . Now,  $L_1 = R_0$  and in order to obtain  $R_1$ ,  $R_0$  which is 32-bit is expanded using an expansion table (refer to Appendix A) to 48-bits. The resulting 48-bits is exored with  $K_1$  generating a 48-bit output which is divided into 8 group of 6-bits viz.,  $B_1$ ,  $B_2$ .... $B_6$ . Each

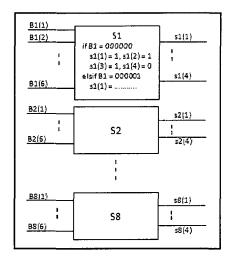

6-bit value is mapped to 8, respective S-boxes  $S_1$ ...... $S_8$  generating a 4-bit value. The mapping is done by considering the first and the sixth bit of say  $B_1$ , and the 2-bits are collectively considered to be row number and the remaining four bits from  $2^{nd}$  bit to  $4^{th}$  bit are collectively considered as column number. By using the row and the column numbers, a 4-bit value is taken from the S-box,  $S_1$  for  $B_1$  in this case. So, combining all the 8, 4-bit outputs of 8, single S-boxes, we get a 32 bit output. This 32-bit output is subjected to permutation by a table P and then exored with  $K_1$  and is denoted as f.  $R_1$  is obtained from f and  $L_0$  by exoring both the 32-bits.

The above procedure represents one round of calculations. The entire DES algorithm has 16 such rounds using the two important equations mentioned above, starting from  $L_0$ ,  $R_0$  until the generation of  $L_{16}$ ,  $R_{16}$ .  $L_{16}$  which represents the left 32-bits and  $R_{16}$  which represents the right 32-bits are flipped and subjected to final permutation  $IP^{-1}$  and the resulting output is the cipher text. As we know the entire procedure of DES, let's move on to investigate how DES is implemented on hardware.

#### 1.2 Implementations of DES on FPGA

Since the creation of DES there have been many implementations of the algorithm. The most common implementation is the software implementation. Software implementation provides a great flexibility but it is slow for those applications where execution time is a crucial factor. Another implementation of DES is the ASIC (Application Specific Integrated Circuit) implementation. Execution speed is a major advantage of this method. ASICs have higher cost of implementation since they have to follow expensive and time-consuming fabrication process. Reconfigurable logic like the FPGA has the dual advantage of the software implementation and the ASIC

implementation. FPGAs are faster and have high flexibility and could be reconfigured or reprogrammed any number of times. They have the advantage to be programmed with different designs or modifications of the same design hence reducing the time and cost of implementing a design.

There are different synchronous DES designs which have been implemented on FPGAs [6-8]. In some of the designs, 16 sub-keys are pre-computed and multiplexers are used to select each sub-key. In comparison with the lookup table approach to implement the S-boxes, the direct implementation of Boolean functions increased the speed of processing, saved on the number of gates and was more suitable for FPGA architectures [6]. A design using pipelining approach and ROM elements present in the FPGA could achieve 1Gbps. DES with 16 pipelines gave the maximum speed but occupies more area in the FPGA [7]. The overall security of the design was improved by using different keys every clock cycle [8]. The fastest synchronous DES implementation on FPGA runs a data rate of 10.7 Gbps, utilizes Jbits on a FPGA. Jbits provides a Java-based Application Programming Interface (API) for the run-time creation and modification of the configuration bit-stream. This design is not a single-chip implementation of the full DES algorithm since the key schedule is computed in software. Also, it can only accommodate one key per data transfer session [9].

Here are some of the conclusions made when a DES design was implemented on a FPGA. S-Boxes should be implemented in ROM elements for maximum performance. Bigger chip results in a slower design. A migration from speed grades -4 to -3, -3 to -2 and -2 to -1 result in up to 20% higher performance. The Xilinx device is faster than the

Altera device even if the former is bigger than the later and had a slower speed grade (-4) than the second which had the faster speed grade (-1) [7].

#### 1.3 Asynchronous Design Methodology

Logic design methods can be broadly classified into two categories, namely synchronous and asynchronous methodologies. Synchronous method is the commonly used method where the data is available to all the components of the design at the rising edge or at the falling edge of the clock. The clock signal is the dictator for the entire circuit's operation. In the asynchronous methodology there is mutual understanding between the neighboring units of the design. Sutherland [10] used a metaphor of the bucket brigade to explain the difference between the two methodologies.

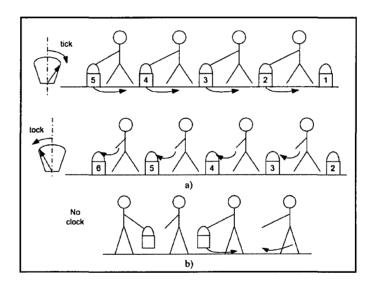

Figure 1.2 Metaphor of the bucket brigade a) Synchronous b) Asynchronous

Asynchronous circuits have several potential advantages over their synchronous counterparts. Clock skew is a matter of concern in synchronous logic but doesn't affect asynchronous logic since the methodology doesn't use a clock at all. Asynchronous circuits have average case performance unlike synchronous circuits whose clock is set according to worst case delay due to which asynchronous designs are faster than the

synchronous designs. Another advantage of asynchronous designs is that these have high energy efficiencies. Asynchronous circuits eliminate glitches and have transitions on the computation path where and when involved in the current computation thereby decreasing energy consumption. These designs also have robust external input handling capability since there is no clock which determines the inputs at a particular time. Hence, asynchronous circuits can accommodate inputs effectively. Asynchronous circuits have better noise and EM properties when used in mixed-signal circuits.

Asynchronous circuits can even utilize a synchronous wrapper, such that the end user does not know that the internal circuitry is actually asynchronous in nature. International Technology Roadmap for Semiconductors (ITRS) envisions a likely shift from synchronous to asynchronous design styles in order to increase circuit robustness, decrease power, and alleviate many clock-related issues. ITRS also states that asynchronous circuits will account for 19% of chip area within the next 5 years, and 30% of chip area within the next 10 years [11].

#### 1.4 Soft Errors and Digital Circuits

Soft errors are random nonrecurring single bit errors in memory devices, including SRAM, DRAM, registers, and latches. Alpha particles from decaying uranium and thorium impurities in integrated circuit interconnect and packaging is a major source of soft errors at sea level and the neutron flux from cosmic rays is the major cause at higher altitudes [12]. The intensity of these soft errors depends on the energy of the incoming particle, location of the device, the geometry of the impact, the location of the strike, and the design of the logic circuit.

For applications in medical electronic devices this soft error mechanism may be extremely important. Neutrons are produced during high energy cancer radiation therapy using photon beam energies above 10 MV. These neutrons are moderated as they are scattered from the equipment and walls in the treatment room resulting in a thermal neutron flux that is about  $40 \times 10^6$  higher than the normal environmental neutron flux. This high thermal neutron flux will generally result in a very high rate of soft errors and consequent circuit upset [13-14].

The incoming particle must be strong enough to induce a charge that can change the voltage value. The minimum charge required to change the logic level is called critical charge denoted as  $Q_{crit}$ . As device sizes are scaling down, the devices are prone to soft errors for lesser  $Q_{crit}$ .

The location of the device also influences the number of particle strikes and their effects. For example, the effect of soft error is worse in places father to equator compared to places on the equator and worse in mountain tops rather than at sea level due to the density of cosmic rays.

Both synchronous and asynchronous circuits are affected by soft errors. In the case of synchronous circuits, if a soft error occurs during a clock tick, a wrong output is generated. Asynchronous circuits with dual-rail inputs and outputs have better advantages over synchronous circuits to detect and correct soft errors. This thesis focuses only on the soft errors generated in asynchronous combinational logic. Soft error rate (SER) is the rate at which a device or system encounters or is predicted to encounter soft errors. It is typically expressed as either number of failures-in-time (FIT), or mean-time-between-failures (MTBF). The unit adopted for quantifying failures in time is called FIT,

equivalent to 1 error per billion hours of device operation. MTBF is usually given in years of device operation. To put it in perspective, 1 year MTBF is equal to approximately 114,077 FIT [15].

Soft errors were first discovered in memory elements like DRAMs in 1970s. Since then DRAMs were the focus for soft errors also because it occupies most of the susceptible surface area. DRAMs of 256 Kb with 1980s technology had flips of five to six bits from a single alpha particle [15]. The present day devices must have many more flips for the same alpha particle. Error-correcting codes [16] are used to deal with soft errors in memory elements. Due to the continuous scaling down of the device sizes attention has been shifted from memories to combinational logic circuits [17]. Soft error detection and correction in combinational logic is an ongoing research topic since efficient soft error tolerant designs are not available. Logic soft errors are very significant contributors to system-level silent data corruption for designs manufactured in advanced technologies (90nm, 65nm, onwards) and targeted for enterprise computing and communications applications [18]. The model described by P. Sivakumar, to compute the SERs for existing and future microprocessor-style designs predicted that the SER per chip of logic circuits will increase nine orders of magnitude from 1992 to 2011 and at that point will be comparable to the SER per chip of unprotected memory elements [4].

#### 1.5 Thesis objectives

This thesis concentrates purely on asynchronous methodology. The asynchronous methodology used here is Null-Convention Logic (NCL) and is explained in detail in Chapter II. The thesis also includes FPGA designs and usage of different FPGAs. The

topic of soft error detection and correction is also discussed. The major objectives of the thesis are:

- 1) Designing an asynchronous model of DES algorithm using NCL dual-rail logic and simulating the design and addressing different issues in synthesizing the asynchronous DES design on different FPGAs.

- 2) Improving the asynchronous DES design to optimally utilize the resources on the FPGA chip.

- 3) Designing an NCL dual-rail logic circuit which can efficiently detect and correct the occurrence of soft errors in asynchronous circuits.

- 4) Synthesizing the above mentioned circuit on FPGA and testing the circuit using hardware components.

- 5) Adding the soft error tolerant circuit to one of the asynchronous DES rounds and testing its operation.

#### CHAPTER II

#### BACKGROUND WORK ON NULL CONVENTION LOGIC

Asynchronous circuits can be grouped into two main categories: bounded-delay and delay-insensitive (DI) models. Bounded-delay models assume that delays in both gates and wires are bounded which leads to extensive timing analysis of worse-case behavior to ensure correct circuit operation. Delay-insensitive circuits assume delays in both logic elements and interconnects to be unbounded, although they assume that wire forks within basic components, such as a full adder, are isochronic, meaning that the wire delays within a component are much less than the logic element delays within the component, which is a valid assumption in the future nanometer technologies. Wire connecting components do not have to adhere to the isochronic fork assumption which enables them to operate in the presence of indefinite arrival times for the reception of inputs.

NCL [19] is a delay-insensitive asynchronous paradigm, which means that NCL circuits will operate correctly regardless of the delay of components and wires. NCL circuits utilize dual-rail or quad-rail logic to achieve delay-insensitivity. Throughout the thesis, the designs make use of dual-rail logic. This chapter explains the basics of NCL such as the components used to construct NCL circuits, criteria that each and every component of the NCL dual-rail signals must possess and transistor level construction of the basic components of NCL circuits.

#### 2.1 Completion Criteria

NCL uses two completeness criteria to achieve its delay-insensitive behavior: symbolic completeness of expression and completeness of input. A symbolically complete expression is defined as an expression that only depends on relationships of the symbols presented in the expression. Dual-rail signals with three logic states (NULL, DATA0, and DATA1) are used to achieve symbolic completeness of expression. A dual-rail signal D consists of two wires,  $D^0$  and  $D^1$ . The value of a dual-rail signal is represented by a value from the set {DATA0, DATA1, NULL}, shown in Table 2.1. The DATA0 state ( $D^0$ =1(high),  $D^1$ =0(low)) corresponds to a Boolean logic 0. The DATA1 state ( $D^0$ =0(low),  $D^1$ =1(high)) corresponds to a Boolean logic 1. Null state ( $D^0$ =0(low),  $D^1$ =0(low)) corresponds to non- data state. The state where  $D^0$ =1(high) and  $D^1$ =1(high) is forbidden.

Table 2.1 Dual-rail encoding

| Logic Value | Encoding |       |

|-------------|----------|-------|

|             | $D^0$    | $D^1$ |

| DATA1       | 0        | 1     |

| DATA0       | 1        | 0     |

| NULL        | 0        | 0     |

| Invalid     | 1        | 1     |

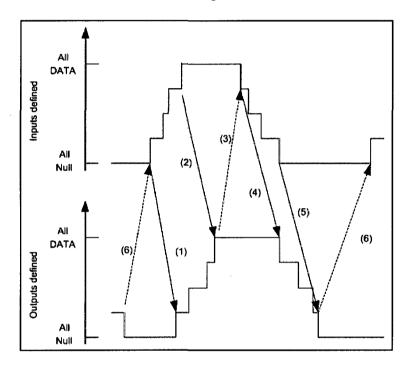

The second criterion, completeness of input, states that for an NCL combinational circuit, 1) the output may not transition from NULL to a complete set of DATA until the input values are completely DATA and 2) the output may not transition from DATA to a complete set of NULL values until the input values are completely NULL. The criterion, equivalent to Seitz's "weak condition" [20], is illustrated in figure 2.1. This criterion is a necessary condition for speed-independence. The orderings labeled in figure 2.1 are explained below.

- (1) Some inputs become DATA before some outputs become DATA.

- (2) All inputs become DATA before all outputs become DATA.

- (3) All outputs become DATA before some inputs become NULL.

- (4) Some inputs become NULL before some outputs become NULL.

- (5) All inputs become NULL before all outputs become NULL.

- (6) All outputs become NULL before some inputs become DATA.

Figure 2.1 Weak conditions for NCL completeness of input.

An output is said to be input-complete with respect to a particular input if the output value (DATA) is not available until the input value (DATA) is available. And this input is a complete input of this particular output. A combinational circuit is input-complete if and only if each input at least has one output that is input-complete with respect to it.

#### 2.2 Threshold Gates with Hysteresis

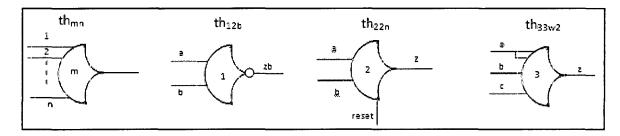

NCL uses a special type of gates, namely threshold gates with hysteresis [21] [22]. A general name of a fundamental threshold gate is described as thmnWn<sub>1</sub>n<sub>2</sub>....n<sub>w</sub>, where 'th' means that the gate is a threshold gate, m is the threshold, n is the number of inputs, W means that the following number 'n<sub>1</sub>', 'n<sub>2</sub>', ... 'n<sub>w</sub>' are weights of the first 'W' inputs and the weights of other inputs are one by default. Some of the threshold gates are shown in figure 2.2. In some threshold gates there could be variation for set, reset or inverted output. In that case letter 'd', 'n', or 'b' can be attached to the name of the threshold gate. For example, th<sub>22n</sub> is a th<sub>22</sub> gate with a control input 'reset' so that the output is initialized to low as long as 'reset' signal is active. Similarly, 'd' is used to initialize the output to high and 'b' indicates that the gate generates an inverted output.

Figure 2.2 Different threshold gates

The threshold behavior of the threshold gate requires that the output become 1 if at least m of n inputs have become 1. The hysteresis behavior requires that the output only changes after a sufficiently complete set of input values have been established. In the case of a transition from a 0 to 1, the output remains at 0 until atleast m of the n inputs become 1. In the case of a transition from 1 to 0, the output remains at 1 until all n inputs become 0. The hysteresis within each NCL gate ensures that all inputs must transition to NULL before a combinational circuit's output will transition to NULL, making the circuit input-complete with respect to NULL, assuming that the circuit is input-complete

with respect to DATA. These gates are the basic components upon which all the other essential components of an NCL pipeline (discussed in 2.3) are built.

There are 27 fundamental threshold gates in the NCL design library, as shown in Table 2.2, which constitute the set of all functions consisting of four or fewer variables.

Table 2.2 Twenty seven fundamental NCL gates and their Boolean functions

| ** |                      |                             |

|----|----------------------|-----------------------------|

|    | NCL gate             | Boolean Function            |

|    | th <sub>12</sub>     | A + B                       |

|    | th <sub>22</sub>     | AB                          |

|    | th <sub>13</sub>     | A + B + C                   |

| l  | th23                 | AB + AC +BC                 |

|    | th33                 | ABC                         |

|    | th <sub>23W2</sub>   | A + BC                      |

|    | th33w2               | AB + AC                     |

|    | th <sub>14</sub>     | A + B + C + D               |

|    | th <sub>24</sub>     | AB + AC + AD + BC + BD + CD |

|    | th <sub>34</sub>     | ABC + ABD + ACD + BCD       |

|    | th44                 | ABCD                        |

|    | $th_{24W2}$          | A + BC + BD + CD            |

|    | $	h_{34W2}$          | AB + AC + AD + BCD          |

|    | $th_{44W2}$          | ABC + ABD + ACD             |

|    | th34W3               | A + BCD                     |

|    | th <sub>44W3</sub>   | AB + AC + AD                |

|    | $th_{24W22}$         | A + B + CD                  |

|    | th <sub>34W22</sub>  | AB + AC + AD + BC + BD      |

|    | th <sub>44W22</sub>  | AB + ACD + BCD              |

|    | th <sub>54W22</sub>  | ABC + ABD                   |

|    | th <sub>34W32</sub>  | A + BC + BD                 |

|    | th <sub>54W32</sub>  | AB + ACD                    |

|    | th <sub>44W322</sub> | AB + AC + AD +BC            |

|    | $	h_{54 m W322}$     | AB + AC + BCD               |

|    | th <sub>xor0</sub>   | AB + CD                     |

|    | th <sub>and0</sub>   | AB + BC + AD                |

|    | th <sub>24comp</sub> | AC + BC + AD + BD           |

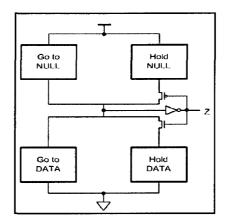

#### 2.3 NCL Pipeline

The framework for NCL systems consists of delay-insensitive combinational logic sandwiched between delay-insensitive registers. This combination of NCL registers along with completion detection circuitry and combinational logic is called NCL pipeline [23]. So, the basic components of any NCL circuit or system are NCL registers,

completion detection circuitry and NCL combinational logic like exor, full-adder, etc. Figure 2.3 provides the pictorial representation of an NCL pipeline.

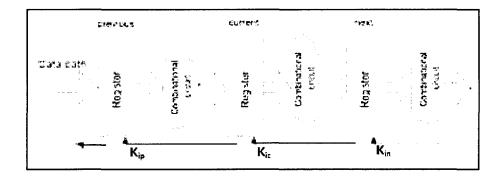

Figure 2.3 Basic NCL pipeline structure

DATA and NULL pairs pass through each of the components in the NCL pipeline consecutively. The presence of NULL is used as time reference in NCL circuits. The input request for each register comes from the completion detection circuit of the next register. Assume that all the circuits are in a NULL state and that the input request signals of the current register (K<sub>ic</sub>) and the next register (K<sub>in</sub>) are requesting a DATA wavefront and the previous register is presenting a complete DATA set to its combinational circuit. As the wavefront propagates through the previous combinational circuit to the current register, the current register passes the data since its control line is requesting DATA. When a complete data set is recognized by the current detection circuitry, it transitions its control line (K<sub>ip</sub>) to the previous register to request NULL indicating that the current register has received and stored the data wavefront and the previous register can pass a NULL wavefront. The requested NULL wavefront from the previous register can arrive at the current register but, as long as its (current register's) control line ( $K_{ic}$ ) is requesting DATA, the NULL wavefront will be blocked and the current register will maintain presentation the set of DATA values to the current combinational circuit. The control line for the current register will remain requesting DATA until the DATA wavefront has propagated through the current circuit and has been received by the next register. When the next register receives and stores the DATA wavefront, the DATA set no longer needs to be maintained by the current register. The next completion detection circuit detects the complete DATA set and transitions it's acknowledge  $line(K_{ic})$  to request NULL indicating that it has received the DATA wavefront and the current register can allow a NULL wavefront. This is the entire operation of the whole NCL pipeline.

#### 2.3.1 NCL Register

NCL systems contain at least two delay-insensitive registers, one at the input and the other at the output. Two adjacent register stages interact through their request and acknowledge signals; Ki and Ko, respectively, to prevent the current DATA wavefront from overwriting the previous DATA wavefront, by ensuring that the two DATA wavefronts are always separated by a NULL wavefront.

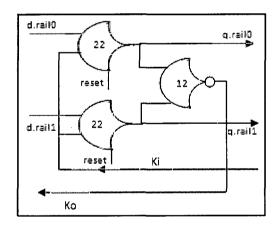

Figure 2.4 1-bit NCL register

Figure 2.4 shows a 1-bit NCL register. An n-bit register is realized through cascaded arrangements of n, 1-bit dual-rail registers. Each 1-bit NCL register used throughout the thesis comprises of two th<sub>22n</sub> gates that pass a DATA value at the input only when Ki (request signal) is logic 1 and pass NULL only when Ki is logic 0. The

register also contains a th<sub>12b</sub> gate which has two inputs one of which is connected to the output of one of the two th<sub>22n</sub> gates and the other input is connected to the output of other th<sub>22n</sub> gate. The output of th<sub>12b</sub> is denoted as Ko, the acknowledge signal of the 1-bit register. Ko becomes logic 0 when the register receives complete DATA and has logic 1 when the register receives NULL. The acknowledge signals of each 1-bit register in an n-bit register are combined in the completion detection circuitry to produce the request signal to the previous register stage. The request signal Ki of the current register is from the output of the completion detection circuitry of the next register. Since both the th<sub>22</sub> gates in the 1-bit register are reset to NULL (th<sub>22n</sub>), the register outputs zeros when the reset signal or input is high. However, either register could be instead reset to a DATA value by replacing exactly one of the th<sub>22n</sub> gates with a th<sub>22d</sub> gate. But for the applications in this thesis only th<sub>22n</sub> gates are used.

#### 2.3.2 Completion Detection Circuitry

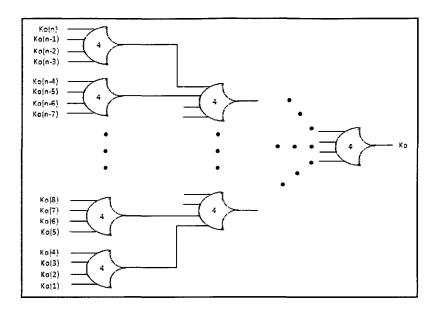

Completion detection circuitry consists of set of gates which determine the complete arrival of DATA or NULL at the registers. As mentioned in the previous section, all the Kos of each 1-bit register goes through the completion detection circuitry and produces the request signal for the previous register. Figure 2.5 is an example of an n-bit completion detection circuit.

Since the maximum input threshold gate is the th<sub>44</sub> gate, the number of logic levels in the completion component for an n-bit register is given by log<sub>4</sub>n. For example, suppose a 64-bit register. The completion detection circuitry has log<sub>4</sub>64=3 levels. In the first level the circuit has 16, th<sub>44</sub> gates, in the second level the circuit has 4, th<sub>44</sub> gates and the third level has 1, th<sub>44</sub> gate.

Figure 2.5 n-bit completion detection circuitry

Here is another example which clarifies the process of constructing the completion detection circuitry in a better way. Consider a 44-bit NCL register. The completion detection circuitry of this 44-bit register has three logic levels and is constructed using 11, th<sub>44</sub> gates in the first logic level, 2, th<sub>44</sub> gates and 1, th<sub>33</sub> gate in the second logic level and 1, th<sub>33</sub> gate in the third logic level.

#### 2.3.3 NCL Combinational Circuit

The functionality of NCL combinational circuits are similar to Boolean combinational logic circuits except that NCL circuits are made from the 27 threshold gates mentioned in table 2.2. All the NCL combinational circuits must maintain two vital properties viz., input-completeness and observability.

Input-completeness requires that all outputs of a combinational circuit may not transition from NULL to DATA until all inputs have transitioned from NULL to DATA, and that all outputs of a combinational circuit may not transition from DATA to NULL until all inputs have transitioned from DATA to NULL.

Observability requires that no orphans may propagate through a gate. An orphan is defined as a wire that transitions during the current DATA wavefront, but is not used in the determination of the output. Orphans are caused by wire forks and can be neglected through the isochronic fork assumption (i.e. gate delays are much longer than wire delays within a component), as long as they are not allowed to cross a gate boundary. This observability condition, also referred to as indicatability or stability, ensures that every gate transition is observable at the output; which means that every gate that transitions is necessary to transition at least one of the outputs.

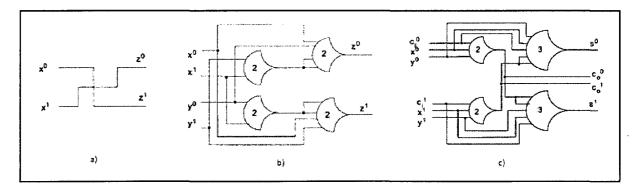

Figure 2.6 shows some of the NCL combinational circuits a) inverter, b) exor and c) full-adder using threshold gates. Exor is used in the thesis while constructing DES algorithm using dual-rail logic and full-adder is taken as an example for combinational circuit to demonstrate the working of soft-error detection and correction circuitry.

Figure 2.6 NCL implementation of a) Inverter b) Exor gate c) Full-adder [24]

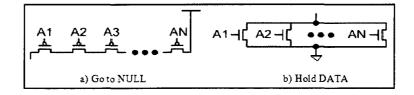

# 2.4 NCL Circuits using CMOS Transistors

An efficient method is to design the threshold gates with hysteresis using CMOS technology at transistor level. There are three different ways of realizing a threshold gate using transistors. These are static, semi-static and dynamic. Static gates are the stable transistor level threshold gates while semi-static and dynamic can reduce the amount of

area occupied by them. The three designs differ in their structure. The general structure of a static threshold gate is shown in figure 2.7. This thesis doesn't use the transistor level designs of the threshold gates but makes use of their behavioral description using VHDL. This section is basically for understanding the concepts of threshold gates at transistor level.

Figure 2.7 General structure of a static gate

The Go to NULL and Hold DATA blocks are complementary to each other and have the universal forms shown in figure 2.8. Go to NULL block is only ON when all N inputs are 0 and Hold DATA block is ON if one or more of the inputs are 1. Because of the series chain in the Go to NULL block, speed considerations will limit these structures to a maximum number of inputs, typically less than six. The structures of Go to DATA and Hold NULL are complementary to each other and depends on the particular threshold gate.

Figure 2.8 Go to NULL and Hold DATA transistor blocks

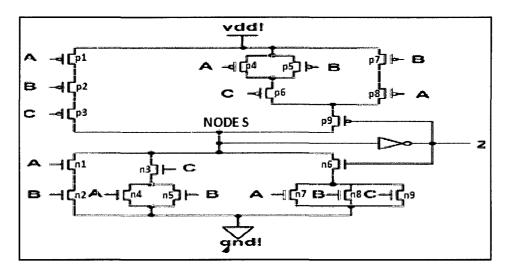

Figure 2.9 is a schematic of a transistor realized static th<sub>23</sub> gate. This gate has three inputs and the output is asserted only if atleast two of the inputs are asserted. Node S shown in the figure is called the sensitive node.

Figure 2.9 Static th<sub>23</sub> gate

All the components in the NCL circuit design are made up of these threshold gates which could be realized using CMOS transistors. So each component, be it an NCL register, completion detection circuitry or combinational logic, is a collection of these threshold gates.

#### CHAPTER III

#### NCL CIRCUIT DESIGN WITH VHDL

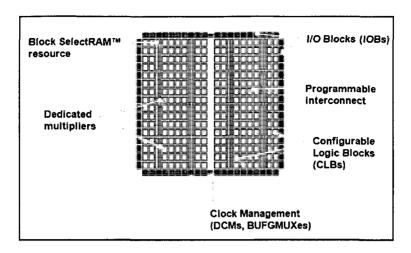

An FPGA is a semiconductor device that can be programmed or configured any number of times using a schematic design or a source code in HDL (hardware description language) that describes the user's hardware design. The NCL circuit designs using HDLs could be used on these existing CAD tools for synchronous circuits [25]. In order for the FPGA to be programmed with NCL circuits, the VHDL (VHSIC (Very High Speed Integrated Circuit) Hardware Description Language) description of these circuits is necessary. The first part of this chapter gives details about FPGA. The design flow used in construction of these NCL circuits until they are programmed on the reconfigurable logic is explained in the next section followed by the internal details of each essential unit used for constructing NCL circuits. The fourth section details an example of a simple NCL circuit and its simulation using the software.

#### 3.1 FPGA

The basic resources present in an FPGA are CLBs (configurable logic blocks which contain combinational logic and register resources), IOBs (input/output blocks and are the interface between FPGA and outside world), PIs (programmable interconnections), RAM blocks and other resources like three-state buffers, global clock buffers, boundary scan logic, dedicated multipliers, digital clock managers, etc. Figure 3.1 shows the basic resources present inside an FPGA.

Figure 3.1 Basic resources of an FPGA [26]

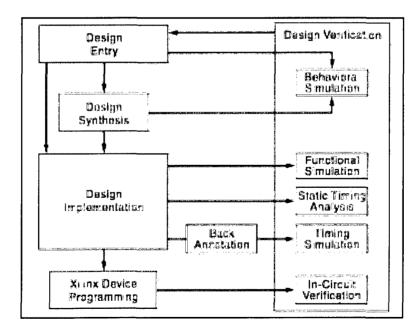

The basic design steps to configure an FPGA are shown in figure 3.2. These are the design entry, design synthesis, design implementation, and device programming. Design verification, which includes both functional verification and timing verification, takes places at different points during the design flow.

Figure 3.2 FPGA design flow [27]

Design entry is the first and foremost step in the design process to configure an FPGA. This step involves the creation of design files using schematic editor or HDL

(Hardware Description Language) and is referred to as RTL (Register Transfer Level). In RTL design, a circuit's behavior is defined in terms of the flow of signals (or transfer of data) between hardware registers, and the logical operations performed on those signals. Automatically creating lower level of logic abstraction from higher level of logic abstraction is what design synthesis is all about. In this design process an RTL description is usually converted to a gate-level description of the circuit by a logic synthesis tool. The next step is the design implementation. This step comprises of three steps; translation, mapping and place and routing. Merging multiple design files into a single netlist is called translation. Mapping is nothing but assigning a logic element to a physical element. Mapping logic onto the specific locations in the target FPGA chip, connecting the components and extracting timing data into reports is place and route. The design is verified at different levels in this process. Checking the syntax, functional simulation and timing simulation are some of the verification procedures. Once all the above steps are successfully performed there is the much awaited final step called programming or configuring the device. This involves creating a file that the FPGA can understand, for example, a .bit file in the case of Xilinx FPGAs or .sof file in for Altera FPGAs and downloading the file to the FPGA.

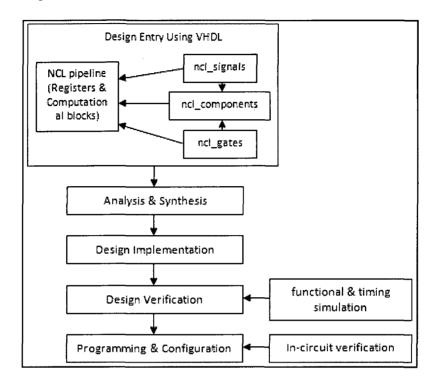

## 3.2 Design Flow used in the Thesis

Figure 3.3 illustrates the design flow used in the thesis starting from how the concept of dual-rail logic has been introduced into the design construction all the way through programming the FPGA with the constructed design. In order to configure the FPGA with NCL circuits, the design entry step must be performed using a HDL. VHDL

(VHSIC (Very High Speed Integrated Circuits) hardware description language) is the language used throughout the thesis.

Figure 3.3 Design flow

The design entry step deals with the construction of NCL pipeline which includes NCL dual-rail registers and the NCL dual-rail computational blocks present between them. The way the NCL dual-rails circuits are constructed is clearly described in section 3.3. Once the circuits are designed, these circuits are undergone compilation using Quartus II software which include analysis & synthesis and design implementation. Now, the circuit needs to be verified. So, both functional simulation (no delays included) and timing simulation are performed on the circuit. Once the verification is done, the synthesized design needs to be programmed on an FPGA. Assign I/O pins of the FPGA to the inputs and outputs of the generated design and we are set to program the FPGA with this design. The "program device" option in the Quartus II leads to a window where

\*.sof file is selected to be programmed on the Altera's Cyclone II FPGA present on the DE2 development and education board. Once the built circuit is configured on a FPGA, verification is done by providing inputs generated by components on board and outputs are extracted from the expansion headers of the board and viewed on a logic analyzer.

#### 3.3 NCL Circuits in VHDL

In order to design NCL circuits in VHDL, several components need to be coded first. These components include creating a used defined data-type called the "dual\_rail\_logic", creating generic n-bit NCL dual-rail registers and completion detection circuitry and threshold gates with hysteresis, etc., which are supposed to be building blocks of NCL circuits and aid in constructing any kind of NCL pipeline architecture. This section explains how these individual units are coded and how they are used in constructing NCL pipeline architectures.

# 3.3.1 Data Type called dual\_rail\_logic

VHDL doesn't contain a predefined data-type for the dual-rail logic signals. So, first a user-defined data-type called "dual\_rail\_logic" has been defined which comprises of two std\_logic type signals: Rail0 and Rail1. The data-type also has its vector definition as dual\_rail\_logic\_vector. The user-defined data type is defined in a package called "ncl\_signals" and this package is placed in the work directory and will be accessed by all the further components using dual-rail logic signals. For instance, if a NCL dual-rail full-adder circuit is to be created, then the inputs, X, Y, and Ci to this computational block are dual\_rail\_logic signals which has two std\_logic signals each as (X.Rail0 , X.Rail1) , (Y.Rail0, Y.Rail1) and (Ci.Rail0, Ci.Rail1). In the VHDL file used to describe the behavioral model of full-adder circuit, the "ncl signals" package need to be mentioned as

"use.work.ncl\_signals.all" and X,Y and Ci needs to be declared as dual\_rail\_logic instead of std\_logic or bit, etc. Figure 3.4 gives the code which creates a user-defined data-type called the "dual\_rail\_logic".

```

Library IEEE;

use IEEE.std_logic_1164.all;

package ncl_signals is

type dual_rail_logic is

record

RAIL1 : std_logic;

RAIL0 : std_logic;

end record;

type dual_rail_logic_vector is array (NATURAL range <>) of dual_rail_logic;

end ncl_signals;

```

Figure 3.4 dual\_rail\_logic data-type

## 3.3.2 Threshold Gates with Hysteresis in VHDL

The behavioral models of the required threshold gates with hysteresis are written using VHDL in a file called "ncl\_gates" (refer to Appendix B for all the other threshold gates). A th<sub>22</sub> gate is defined in VHDL and is shown in figure 3.5 as an example.

```

library ieee;

use ieee.std logic_1164.all;

entity th22x0 is

port(a: in std logic;

b: in std logic; .

z: out std logic );

end th22x0;

architecture archth22x0 of th22x0 is

th22x0: process(a, b)

begin

if (a= '1' and b= '1') then

z <= '1';

elsif (a= '0' and b= '0') then

z <= '0';

end if;

end process;

end archth22x0;

```

Figure 3.5 Behavioral description of th<sub>22</sub> in VHDL

The inputs to these threshold gates are individual dual-rail signals which could be either Railo or Rail1 according to the designed circuit and hence are std\_logic signals. For example, the 1-bit dual-rail register in figure 2.4 has one input as Ki signal and the other input (d.railo for the top th<sub>22</sub> and d.rail1 for the bottom th<sub>22</sub>), one of the rails of 'd' which is a dual-rail signal. The "ncl\_gates" file is also needs to be added to the project that is being constructed so that the components built in the current project can access these threshold gates.

### 3.3.3 NCL Dual-Rail Registers & Completion Detection Circuits in VHDL

NCL dual-rail registers and completion detection circuits are described in a VHDL file called "ncl\_components". "ncl\_components" file consists of design units like generic n-bit NCL dual-rail register and n-bit completion detection circuitry along with their internal components defined in it. The design units present in the "ncl\_components" file make use of the "ncl\_signals" package and threshold gates with hysteresis defined in the "ncl\_gates" file. All these files including "ncl\_signals" are presented in Appendix B for reference.

A single bit NCL register has two th<sub>22n</sub> gates and a th<sub>12b</sub> gate as explained in section 2.3.1. So the behavioral description of a single bit register in VHDL should contain the instances of the two gates as shown in figure 3.6. These instances are accessed from the "ncl\_gates" file and since the inputs are dual\_rail\_logic signals, the "ncl\_signals" package declaration needs to be done. An n-bit NCL register is generated by iteratively generating the same instance of 1-bit NCL register the input data length times as shown in figure 3.7.

```

entity ncl register D1 is

generic (initial value: integer := -4); -- 1=DATA1, O=DATA0, -4=NULL

port(D: in dual rail logic;

ki: in std logic;

rst: in std_logic;

Q: out dual_rail_logic;

ko: out std_logic);

end ncl register D1;

architecture arch of ncl register d1 is

signal Qbuf: dual_rail_logic;

component th22nx0

port (a, b, rst: IN std logic;

z: OUT std logic);

end component;

component th22dx0

port (a, b, rst: IN std logic;

z: OUT std logic);

end component;

component th12bx0

port (a, b: IN std_logic;

zb: OUT std logic);

end component;

begin

RstN: if initial value = -4 generate

RO: th22nx0 port map(D.rail0, ki, rst, Qbuf.rail0);

R1: th22nx0 port map(D.rail1, ki, rst, Qbuf.rail1);

end generate;

Rst1: if initial value = 1 generate

RO: th22nx0 port map(D.rail0, ki, rst, Qbuf.rail0);

R1: th22dx0 port map(D.rail1, ki, rst, Qbuf.rail1);

end generate;

RstO: if initial value = 0 generate

RO: th22dxO port map(D.railO, ki, rst, Qbuf.railO);

R1: th22nx0 port map(D.rail1, ki, rst, Qbuf.rail1);

end generate;

Q <= Qbuf;

COMP: th12bx0 port map(Qbuf.rail0, Qbuf.rail1, ko);

end;

```

Figure 3.6 1-bit NCL register in VHDL

Figure 3.7 Creating n-bit register from 1-bit register

The only gates used for any completion detection circuitry are th<sub>22</sub>, th<sub>33</sub>, th<sub>44</sub>. Based on the number of input signals, the number of logic levels must be calculated using log<sub>4</sub>n. This component basically checks if all the inputs are 0s during DATA and 1s during NULL. The code used first calculates the number of logic levels. Then it checks if the number of inputs are multiples of four. If yes then the signals are assigned to th<sub>44</sub> in sets of four. If there are any leftovers from the multiples of four, it checks if they are two or three. If the leftovers are three then, the code assigns them to th<sub>33</sub> or if the leftovers are two then, th<sub>22</sub> will be assigned to the signals. The same process repeats for each logic level. For the code of the completion detection circuitry refer to Appendix B.

## 3.3.4 Constructing Computational Blocks

```

entity fulladder is

port ( a : in dual rail logic vector(1 to 3);

entity exor is

s : out dual_rail_logic_vector(1 to 2)

port( x : in dual rail logic;

y : in dual rail logic:

end fulladder;

z : out dual_rail_logic];

architecture behavioral of fulladder is

signal c0.c1 ; std logic;

architecture Behavioral of exor is

component th23x0 13

signal u1,u2 : std_logic;

port( a: in std_logic;

b: in std_logic;

c: in std_logic;

component th22xn

port ( a: in std logic:

b: in std logic;

z: out std_legic );

z: out std_logic );

end component:

end component;

component th34w2x0 is

component th23v2x0 is

port(a: in std_logic; -- weight 2

port( a: in std_logic; -- weight 2

b: in std legic;

b: in std logic;

c: in std logic;

c: in std logic;

d: in std logic;

z: out std_logic );

z: out std_logic );

end component;

end component:

begin

begin

g1 : th23x0 port map(a(1).rail0,a(2).rail0,a(3).rail0,c0);

g1 : th22x0 port map(y.rail1,x.rail1,u1);

g2 : th23x0 port map(a(1).raill,a(2).raill,a(3).raill,cl);

g2 : th22x0 port map(y.rail0,x.rail1,u2);

g3 : th34w2x0 port map(c1,a(1).rail0,a(2).rail0,a(3).rail0,s(2).rail0);

g3 : th23u2x0 port map(u1, y.rai10, x.rai10, z.rai10);

g4 : th34w2x0 port map(c0,a(1).rail1.a(2).rail1.a(3).rail1.s(2).rail1);

g4 : th23u2x0 port map(u2, y.rail1, x.rail0, z.rail1);

s(1).rail0<=c0;s(1).rail1<=c1;

end Behavioral;

end behavioral;

b)

```

Figure 3.8 VHDL code for a) Exor gate b) Full-adder

One of the essential parts of an NCL pipeline is the computational block. A computational block is a combinational logic which performs some operations on the inputs generating outputs and is sandwiched between two NCL dual-rail registers. This thesis makes use of only two combinational circuits; the exor gate and the full-adder.

These computational blocks are constructed using the threshold gates with hysteresis and dual\_rail\_logic signals. The schematics of the NCL dual-rail exor gate and full-adder are provided in figure 2.6 and the VHDL behavioral descriptions are provided in the below figure 3.8.

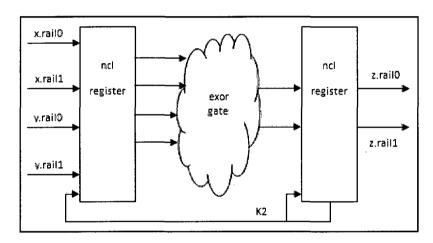

## 3.4 Simulation of a Simple NCL Pipeline

This section explains in detail the procedure how a simple NCL pipeline is created and simulated using Quartus II software. The pipeline considered has two NCL dual-rail register with an NCL dual-rail exor gate as the computational unit between them as shown in figure 3.9.

Figure 3.9 NCL pipeline with exor gate

The very first step is to create a 'New Project' using 'New Project Wizard' in Quartus II [28] (Quartus II tutorial provides all the information on how to compile the designs and program an FPGA). Select a 'New' from the 'file' menu and select 'VHDL file'. In the file write the following code shown in figure 3.10 and save it as 'exor.vhd'. In similar way add the other VHDL files; 'initreg.vhd', 'finalreg.vhd' and 'exor\_dl.vhd' required for the 'exor.vhd' file and these files are presented in figure 3.11. 'initreg.vhd' has two components 'ncl register D' which is a generic n-bit register present in

'ncl\_components' file mentioned earlier and 'th22x0' is th<sub>22</sub> threshold gate which is acting as the completion detection unit for this register. The behavioral description of this gate is present in 'ncl\_gates' file. 'finalreg.vhd' has one component which is 1-bit NCL register called ncl component D1 and is also described in 'ncl components' file.

```

library ieee;

use ieee.std logic 1164.all;

use work.ncl_signals.all;

entity exor is

port ( x : in dual_rail_logic;

y : in dual rail logic;

rst : in std logic;

z : out dual rail logic);

end exor;

architecture behavioral of exor is

signal m,n: dual rail logic vector(1 to 2);

signal zo: dual rail logic;

signal k1,k2: std logic;

component initreg is

port ( D : in dual rail logic vector(1 to 2);

ki : in std logic;

rst : in std_logic;

Q : out dual rail logic_vector(1 to 2);

ko : out std logic);

end component;

component finalreg is

port ( D : in dual rail logic;

ki : in std logic;

rst : in std logic;

Q : out dual rail logic;

ko : out std logic);

end component;

component exor dl

port(ax : in dual rail logic;

bx : in dual rail logic;

cx : out dual rail logic);

end component;

begin

m(1) <= x; m(2) <= y;

reg1 : initreg port map(m,k2,rst,n,k1);

cb : exor_dl port map(n(1),n(2),zo);

reg2 : finalreg port map(zo,k2,rst,z,k2);

end behavioral;

```

Figure 3.10 VHDL code for the NCL pipeline with exor gate

```

Library IEEE;

Use IEEE.std logic 1164.all;

Use work.ncl signals.all;

entity initreg is

port ( D : in dual rail logic vector(1 to 2);

ki : in std logic;

rst : in std logic;

Q : out dual rail logic vector (1 to 2);

ko : out std logic);

end initreg;

architecture behavioral of initreg is

signal ao : std logic vector(1 to 2);

component ncl register D

generic (width: integer; initial value: integer); -- 1=DATA1, 0=DATA0, -4=NULL

port(D: in dual rail logic vector(width-1 downto 0);

ki: in std logic;

rst: in std logic;

Q: out dual_rail_logic_vector(width-1 downto 0);

ko : out std logic vector(width-1 downto 0));

end component;

component th22x0

port(a: in Std logic;

b: in std logic;

z: out std logic);

end component;

begin

regi : ncl_register_D generic map(width=>2,initial_value=>-4)

port map(D,ki,rst,Q,ao);

cdi : th22x0 port map(ao(2),ao(1),ko);

end behavioral;

```

Figure 3.11a) initreg.vhd

```

library leee;

use meee.std logic 1164.all;

Library FEEE;

use work.ncl signals.all;

Use IEEE.std logic 1164.all;

Use work.ncl_signals.all;

entity exor dl is

port ( ax : in dual_rail_logic;

bx : in dual rail legic;

entity finalreg is

port ( D : in dual_rail_logic;

cx : out dual_rail_logic]:

ki : in std logic;

end exor dl;

rst : in std_logic;

architecture Behavioral of exor dl is

Q : out dual rail legic:

signal u1,u2 : std logic:

ko : out std logich:

component th22x0

end finalreg:

port ( a: in std logic;

b: in std logic;

architecture behavioral of finalreg is

2: out std_logic );

component not register bi

end component:

generic(initial value: integer); -- 1=DATA1, 0=DATA0, -4=NULL

component thaswaxo is

port(D: in dual_rail_logic;

port ( a: in std logic; -- veight 2

ki: in std logic:

b: in std logic;

rst: in std_logic:

e: in std_logic;

Q: out dual real logic;

2: out std logic );

ko: out std_logicj;

end component;

end components

begin

gi : th22x0 port map(bx.rail1,ax.rail1,u1);

reg: : mrl_register_D1 generic map(initial_value=>-4)

g2 : th22x0 port map(bx.rail0,ax.rail1,u2);

port map(D, ki, rst, Q, ko);

g3 : th23w2x0 port map(u1,bx.rail0,ex.rail0,cx.rail0);

end behavioral:

q4 : th23v2x0 port map(u2,bx.rail1,ax.rail0,cx.rail1);

end Behavioral:

b) exor dl.vhd

c) finalreg.vhd

```

Figure 3.11b) exor dl.vhd c) finalreg.vhd

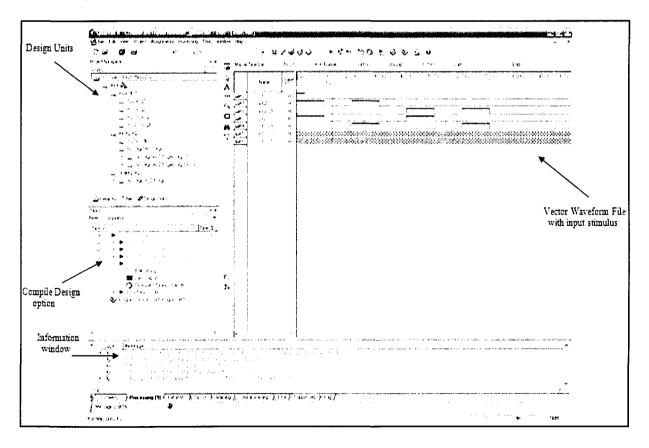

finalreg.vhd doesn't have a separate completion detection unit because it is just a 1-bit register. The output signal from th<sub>12bx0</sub> acts as the completion detection signal. Since the internal component definitions are present in 'ncl\_components' and 'ncl\_gates' these files need to be added to the project by selecting 'add/remove files in project' in the 'project' menu. Since all these components are dual-rail logic, 'ncl\_signals' files must also be added to the project. Once all the required files are present in the project folder, the project needs to be compiled by clicking on the 'compile design' option on the Quartus II software. Check for any syntax error or for any other errors during synthesis and implementation such as I/Os not sufficient for the design or design is too large to fit on to the device, etc.

Figure 3.12 Quartus II Software Window

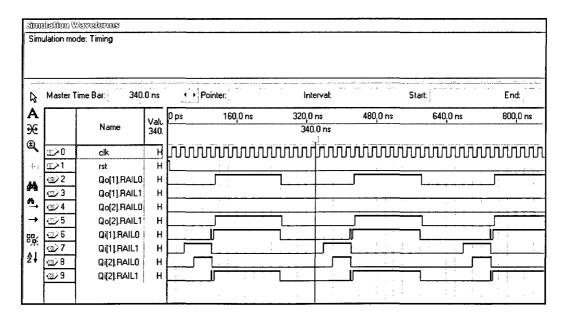

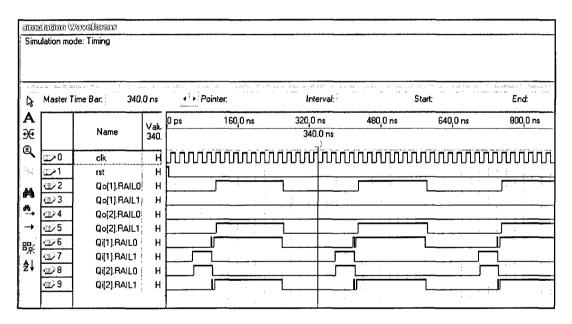

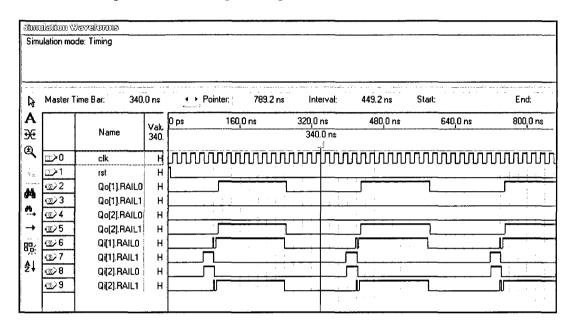

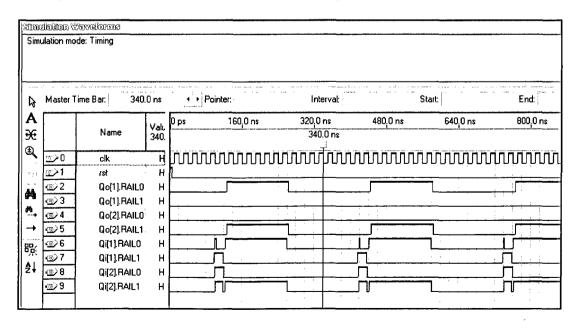

Once the above procedure is done generate a new 'vector waveform file' in order to provide simulation inputs. Add the input and output signals to the 'vector waveform file' and provide appropriate input signals as shown in figure 3.12.

Since the circuit used has dual-rail components, first reset or 'rst' as named in the design need to be asserted. Then the other inputs must be provided as consecutive DATA and NULL pairs. As inputs are provided in the 'vector waveform file' the design needs to be verified or simulated for these inputs. The functional simulation results after simulation is shown in figure 3.13.

Figure 3.13 Simulation results of exor.vhd

#### **CHAPTER IV**

#### ASYNCHRONOUS DATA ENCRYPTION STANDARD ALGORITHM USING NCL

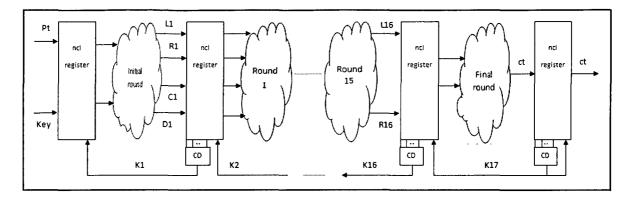

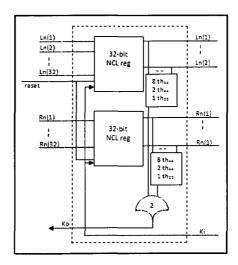

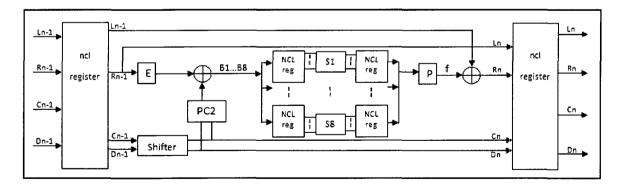

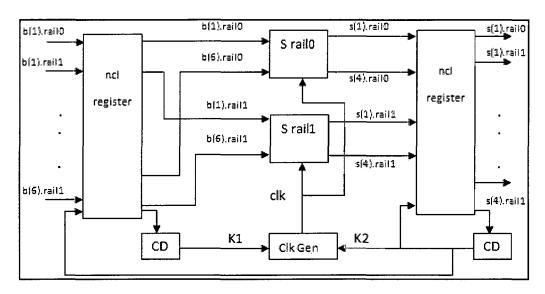

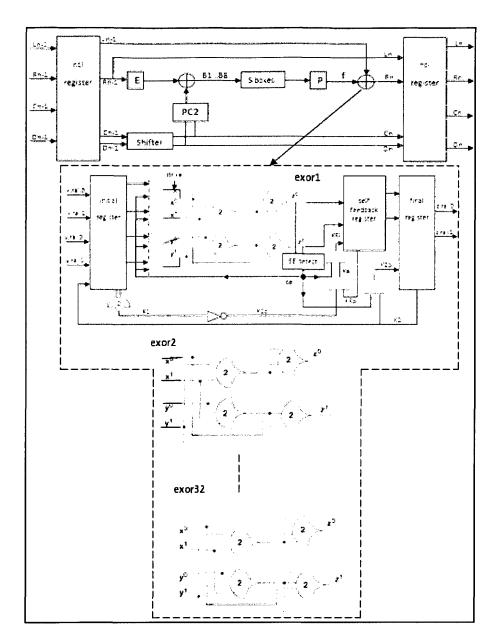

The symmetric property of DES algorithm provides an added advantage to implement DES using NCL dual-rail logic. It creates a scope for the pipelined architecture shown in figure 4.1 where the whole algorithm has 17 combinational logics embedded between NCL registers. The first round has plaintext and key as inputs and L1, R1 and C1, D1 as the outputs. The next round till 15 such rounds have the same combinational logic which takes  $L_{n-1}$ ,  $R_{n-1}$  and  $C_{n-1}$ ,  $D_{n-1}$  as inputs and generates  $L_n$ ,  $R_n$  and C<sub>n</sub> D<sub>n</sub> as outputs. The 16<sup>th</sup> round takes L15, R15 and CD15 as inputs and gives out L16 and R16 as outputs which are then permuted in the 17<sup>th</sup> round to generate the ciphertext output. Altogether, the number of registers present in the asynchronous DES pipeline is eighteen; initial register, NCL registers 1-15, register 16 and final register and the number of combinational logic circuits that are embedded between these eighteen registers are seventeen combinational circuits also called rounds in this case and they are, initial round, rounds 1-14, round 15 and final round. Also, each NCL register has its own completion detection circuitry along with it. The structure of the completion detection circuitry varies as the NCL register structure varies. The details of each component of the DES pipeline are mentioned in the following sections.

Figure 4.1 DES pipeline in NCL dual-rail logic

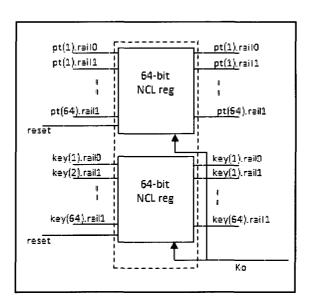

# 4.1 Initial Register

Figure 4.2 Initial Register

The starting stage of the DES pipeline in NCL dual-rail logic is the initial register. This register has plaintext of 64 bits and key of 64 bit dual-rail signals as inputs. Along with these it also has reset signal and Ki signal inputs similar to all the other registers. This initial register is different from the other registers in that it doesn't have a Ko signal since there is no register prior to it. This register will output all zeros when reset signal is logic 1. It allows the plaintext and key values to pass through it when Ki is logic 1. If Ki is logic 0 then the initial register will stop any flow of DATA and will be ready to pass

NULL through it. This register is the only register in the entire DES pipeline that doesn't have a completion detection circuitry. This circuitry has been eliminated to save logic on the FPGA. The structure of initial register is presented in figure 4.2.

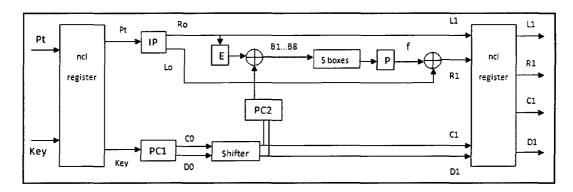

### 4.2 Initial Round

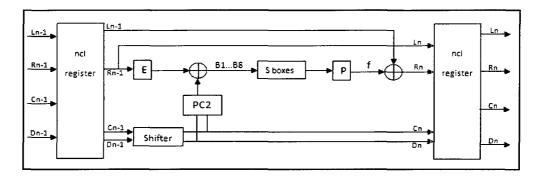

DES pipeline in NCL dual-rail logic starts with an initial register, followed by an initial round. The operations that are performed on the outputs of the initial register are described in figure 4.3.

Figure 4.3 Initial round in the DES pipeline

As soon as the plaintext denoted as pt in figure 4.3 enters the initial round, an initial permutation IP is performed on it and is divided into L0 and R0. The key also undergoes permutation PC1 and is divided into C0 and D0. Shifter is basically used to left shift the bits in C0 and D0 which become C1 and D1 for the next stage and are used to form subkey in the present round. The output of the shifter is concatenated and another permutation PC2 is applied on it. The function E expands R0 from 32 bits to 48 bits as mentioned in the DES algorithm. The outputs of E and PC2 are exored bit by bit using the exor gate designed for NCL dual-rail logic. This is the only dual-rail combinational logic circuit used in the DES algorithm. All the permutations, expansions and left shifts are basically wiring and don't involve any logic function or operation. The output of the

exor gate goes through S-boxes which are constructed using if-else statements addressing all the possible combination of inputs. Eight S-boxes are written in VHDL and the structure of these is shown in figure 4.4 which addresses six-bits of inputs each producing four-bit outputs. The outputs of the S-boxes are combined and then a final permutation P is performed on the bits. The L0 output of IP is then exored with the P output and is fed to the next register as R1 input. The R0 output of the IP becomes the L1 input to the next stage.

Figure 4.4 S-box inputs and outputs

## 4.3 NCL Registers 1-15

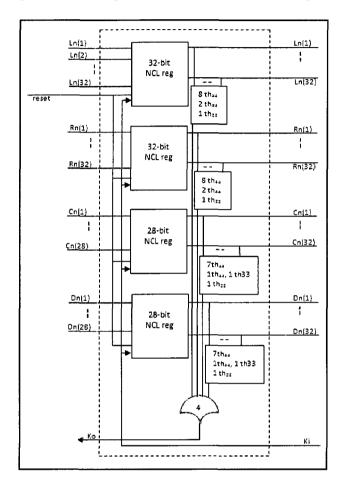

The outputs of the initial round are L1, R1, C1, and D1 which are fed to the next register which takes these signals as inputs. As mentioned earlier the whole DES pipeline consists of fourteen such rounds other than initial round which has the same structure and does similar operations. Due to this reason, the registers governing the rounds on both sides need to be similar, accepting same number of input signals and outputs the same. So NCL registers 1-15 allows Ln, Rn, Cn and Dn (L1, R1, C1, D1......L15, R15, C15, D15) to pass through them. The completion detection circuits for all these registers have four internal circuits which take the Ko signals of each term like Ln, Rn, Cn and Dn. The

four outputs of the four completion detection circuits are fed to a  $th_{44}$  gate, the output of which is the Ko signals (acknowledge signal) for the entire register. The whole structure of the NCL register along with the completion detection circuits is depicted in figure 4.5.

Figure 4.5 The inside view of NCL register 1-15

## 4.4 Rounds 1-14

Asynchronous DES pipeline has fourteen similar rounds which differ only by two functions to initial round. While the initial round has pt, key as inputs and had to permute its inputs, rounds 1-14 has  $L_{n-1}$ ,  $R_{n-1}$ ,  $C_{n-1}$  and  $D_{n-1}$  as inputs and the rounds don't require the initial permutation IP for pt and PC1 for key and is shown in figure 4.6. All the other functions are similar to initial round. Among these fourteen rounds, some of the rounds require a single bit left shift for the  $C_{n-1}$  and  $D_{n-1}$  inputs to form  $C_n$  and  $D_n$  while some

rounds require two bit left shifts. The number of shifts depends on the left shift table as mentioned in Appendix A.

Figure 4.6 Internal structure of rounds 1-14

## 4.5 Round 15